1048576-BIT DUAL-PORT DYNAMIC RAM

### DESCRIPTION

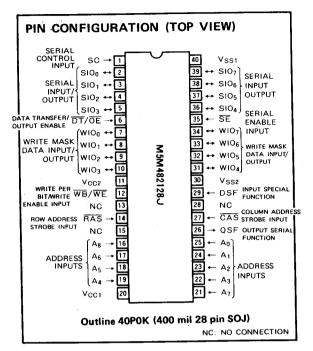

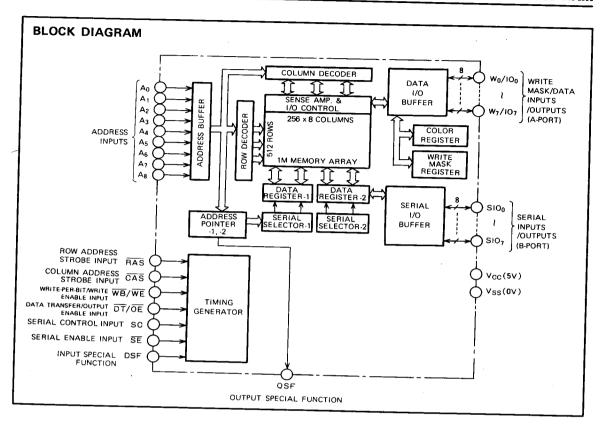

The Mitsubishi M5M482128J is a high speed 1048576-bit Dual Port Dynamic Memory equipped with a 128K x 8 Dynamic RAM Port and a 256 x 8 Serial Read/Write Port. The use of triple-layer polysilicon CMOS process combined with silicide technology and a single transistor dynamic storage cell provide both high circuit density and low power dissipation.

The Serial Read/Write Ports are connected to an internal 2,048 bit Data Register through a 256 x 8 Serial Input/ Output Control circuit and can be serially readout or written in with a clock rate of up to 33MHz.

All reads and writes are done relative to the RAM array, thus Data transfer from the RAM array to the Data Register is referred to as a Read Transfer, while Data Transfer from the Data Register to the RAM array is referred to as a Write Transfer.

### **FEATURES**

| Type name      | RAS<br>Access<br>Time<br>(ns) | Random<br>Read/Write<br>Cycle Time<br>(ns) | Serial<br>Read<br>Cycle Time<br>(ns) | Random<br>Read/Write<br>V <sub>CC</sub> Supply<br>Current<br>(mA) |        |

|----------------|-------------------------------|--------------------------------------------|--------------------------------------|-------------------------------------------------------------------|--------|

| M5M482128J-8   | 80ns                          | 160ns                                      | 30 n s                               | 80 m A                                                            | 60 m A |

| M5M482128J-10  | 100ns                         | 190ns                                      | 30 n s                               | 70 m A                                                            | 50 m A |

| M5M482128 J-12 | 120ns                         | 220ns                                      | 40 n s                               | 60 m A                                                            | 40 m A |

Dual Port Architecture

RAM Port: 128K-word x 8-bit

Serial Port: 256 word x 8-bit

- Bidirectional Data Transfer function between the RAM array and the Data Register.

- Fully Asynchronous Dual Port Accessability (Split SAM)

- Addressable Start of Serial Read/Write (Pointer Control Function)

- Write per Bit Function

- Real Time Data Transfer from the RAM Array to the Data Register.

- Fast Page Mode, Hidden Refresh and CAS before RAS Refresh.

- 512 cycle/8ms Refresh.

- Flash write operation.

- Block write operation

### APPLICATION

Display equipment for personal computer/work station, Frame memory for digital TV/VTR, Videotex, Teletext, Video printer, High Speed data transmission systems.

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

4-78

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

### PIN DESCRIPTION

| Pin                            | Name                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS                            | ROW ADDRESS STROBE                   | It is used as a clock which latches the row address ( $A_0 \sim A_8$ ) to select the word line. It also latches the mask data for Write-per-bit, Flash write and Split write transfer functions when the $\overline{WB}$ level is low. $\overline{CAS}$ before $\overline{RAS}$ refresh mode is activated when preceeded by $\overline{CAS}$ falling low.                                                       |

| CAS                            | COLUMN ADDRESS<br>STROBE INPUT       | It is used as a clock which latches the column address ( $A_9 \sim A_{16}$ ) and initiates the reading or writing of the selected words. In the data transfer cycle, this latches the SAM Top address point. (TAP)                                                                                                                                                                                              |

| A <sub>0</sub> ~A <sub>8</sub> | ADDRESS INPUT                        | The M5M482128 utilizes an address multiplex method for selecting one word among the 128K-word memory<br>cells. 9 row addresses and 8 column addresses are latched by the RAS and CAS falling edge. In the data<br>transfer cycle, this address input is also combined with the serial access start address. (TAP)                                                                                               |

| WB/WE                          | WRITE-PER-BIT/WRITE<br>ENABLE INPUT  | When the WB/WE level is low at the RAS falling edge Write-per-bit (RAM write with mask), Write transfer<br>with MASK or Flash write with MASK cycle is selected. When it is high, normal read/write. Read transfer<br>or Load color register cycle is selected. This clock also controls early/late write mode at the CAS falling edge.                                                                         |

| DT/OE                          | DATA TRANSFER/OUTPUT<br>ENABLE INPUT | When the $\overline{\text{DT}}/\overline{\text{OE}}$ level is low at the $\overline{\text{RAS}}$ falling edge, the data transfer cycle is selected and when it is high,<br>RAM read/write cycle, Load color register cycle or Flash write cycle is activated according to the $\overline{\text{WB}}/\overline{\text{WE}}$<br>and DSF combination. In the RAM read cycle, it enables the data output (RAM port). |

| WIOn*                          | WRITE MASK / DATA<br>INPUT/OUTPUT    | These are the data input/output pins to the RAM. During RAM write-per-bit cycle, Split write transfer cycle<br>or Flash write cycle, high data input at the RAS falling edge enables the selected-bit (row) for write operation.<br>In the write cycle, the data is latched at the falling edge of the CAS or the WB/WE input, whichever is the<br>later.                                                       |

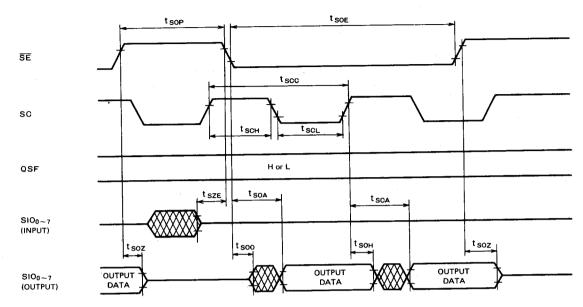

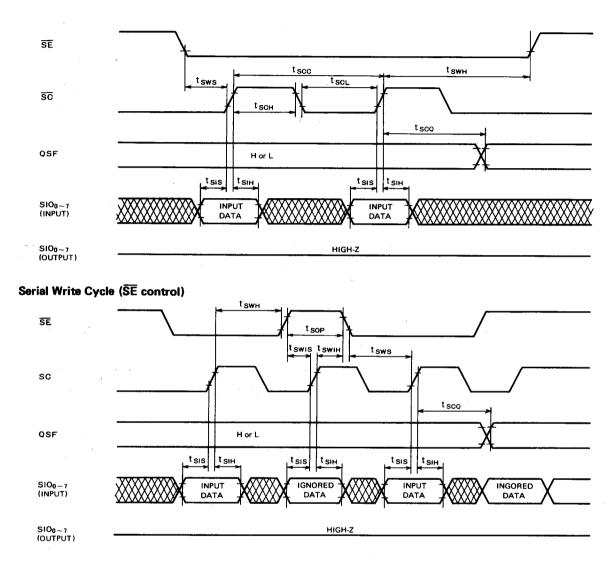

| SC                             | SERIAL CONTROL INPUT                 | All serial access is initiated from the SC clock rising edge. In the serial read cycle, the output data is held until the next clock rise. Also in the serial write cycle, the data is latched at the SC clock rising edge.                                                                                                                                                                                     |

| SIOn*                          | SERIAL INPUT/OUTPUT                  | 256 x 8 word serial data input/output pins.                                                                                                                                                                                                                                                                                                                                                                     |

| SE                             | SERIAL ENABLE INPUT                  | This enables the serial input/output. In the write transfer cycle when SE is high at the RAS falling edge, Pseudo transfer cycle is selected, and when it is low, Write transfer cycle is selected.                                                                                                                                                                                                             |

| DSF                            | INPUT SPECIAL FUNCTION               | This input defines special functions such as Split read/write transfer, Flash write, Block write and Load color<br>register. When it is set low, the device works as a basic dual-port memory except for the Normal write transfer<br>cycle masking mode.                                                                                                                                                       |

| QSE                            | OUTPUT SPECIAL<br>FUNCTION           | Output indicating the serial data selector status.                                                                                                                                                                                                                                                                                                                                                              |

Note \*: n = 0 ~ 7.

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

### 128Kx8 Truth Table

| Code          |     |             | ŘĂ  | 5 falling | ) edge   |                   |             | Ĉ            | AS fall     | ing edg     | e            | Write          |               | F                  | legister           |             |                                       |

|---------------|-----|-------------|-----|-----------|----------|-------------------|-------------|--------------|-------------|-------------|--------------|----------------|---------------|--------------------|--------------------|-------------|---------------------------------------|

| -mnemo<br>nic | CAS |             | WB  | DSF       | SĒ       | Addr              | wion        | WB/WE        | DSF         | Addr        | WIOn         | mask           | Raster<br>op. | Write<br>temporary | mask<br>persistant | Color       |                                       |

| Onting        | 0   | 0           | 0   | 0         | —        | -                 |             |              |             | —           |              |                | —             |                    | —                  | —           | None use                              |

| Option        | 0   | 0           | 0   | 1         | -        | -                 | —           | <u> </u>     | -           | ł           |              | -              | _             | —                  | —                  | —           | C.B.R                                 |

| CBR           | 0   | 0           | 1   | 0         | +        | -                 | -           | -            |             | 1           | -            |                | 1             | _                  | _                  | _           | C.B.R                                 |

| OBIT          | 0   | 0           | 1   | 1         | ·        |                   | —           | —            | _           | —           |              |                |               |                    |                    |             | C.D.N                                 |

| CBR           | 0   | 1           | 0   | 0         | -        | -                 | -           |              | —           | _           |              | _              | _             | _                  | _                  | _           | C.B.R                                 |

|               | 0   | 1           | 0   | 1         | _        | -                 | <b>—</b> .  | -            | -           | -           | _            |                |               |                    |                    |             | 0.5.11                                |

| CBR           | 0   | 1           | 1   | 0         |          | -                 | —           | -            | +           | ł           | —_           | _              | _             | _                  | _                  | _           | C.B.R                                 |

| 0.2.1.        | 0   | 1           | 1   | 1         | -        | _                 | -           | —            |             | _           |              |                |               |                    |                    |             | 0.0                                   |

| м₩Ҭ∕          | 1   | 0           | · 0 | 0         | 9/1      | Row/Ret           | WM1         |              | 0           | ΤΑΡ         |              | Yes            | _             | Load use           |                    | _           | Wr. transfer (SE=0)                   |

| PWT           | 1   | 0           | 0   | 0         | 9/1      | Row/Ref           | WM1         | —            | 1           | TAP         |              | per row        |               |                    |                    |             | Pseudo write transfer (SE=1)          |

| SWT           | 1   | 0           | 0   | 1         |          | Row               | WM1<br>WM1  | _            | 0           | TAP<br>TAP  | -            | Yes<br>per row | -             | Load use           |                    | -           | Split write transfer with<br>new mask |

|               | 1   | 0           | 1   | 0         |          | Row               |             | _            | 0           | TAP         |              |                |               |                    |                    |             | ,                                     |

| RT            | 1   | 0           | 1   | 0         | _        | Row               | _           | _            | 1           | ΤΑΡ         |              | -              |               |                    | -                  | -           | Read transfer                         |

| 0.0.7         | 1   | 0           | 1   | 1         | —        | Row               | -           | Ţ            | - 0         | ΤΑΡ         |              |                |               |                    |                    |             |                                       |

| SRT           | 1   | 0           | 1   | 1         | —        | Row               | —           |              | 1           | TAP         | —            | _              | _             | _                  | _                  |             | Split read transfer                   |

| RWNM          | 1   | 1           | 0   | 0         | <u>·</u> | Row               | <b>W</b> M1 | <b>∗</b> E/L | 0           | Col.        | DQin         | Yes            | -             | Load use           |                    |             | RAM write with new mask               |

| BWNM          | 1   | 1           | 0   | 0         | —        | Row               | WM1         |              | 1           | Col.        | Sel.         | Yes            | -             | Load use           | -                  | Use         | Block write with new mask             |

| FWT           | 1   | 1           | 0   | 1         | -        | Row<br>Row        | WM1<br>WM1  | _            | 0           | -           | -            | Yes<br>per row | -             | Load use           | -                  | -           | Flash write with new mask             |

| RW            | 1   | 1           | 1   | ,<br>0    |          | Row               |             | <b>*</b> E/L | 0           | Col.        | DQin         | _              |               |                    | _                  |             | Read/Write                            |

|               |     | 1           | 1   | 0         |          |                   | _           | <b>#</b> E/L | 1           | Col.        | Sel.         |                |               |                    |                    |             | Block write with no mask              |

|               |     |             |     |           |          | <u> </u>          |             |              |             |             |              |                |               |                    |                    | Use         | DIOCK WITTE WITT TO TIOSK             |

| LCR           |     |             |     |           |          |                   |             |              |             |             |              | _              | _             | -                  | -                  | Load        | Load color reg.                       |

| BW<br>LCR     | 1   | 1<br>1<br>1 | 1   | 1         | -        | Row<br>Ref<br>Ref | _<br>_      |              | 1<br>0<br>1 | —<br>—<br>— | CLR.<br>CLR. | _              | _             | _                  | _                  | Use<br>Load |                                       |

\* E/L: Early write/Late write \*\* Ref: Refresh Address

# FUNCTION

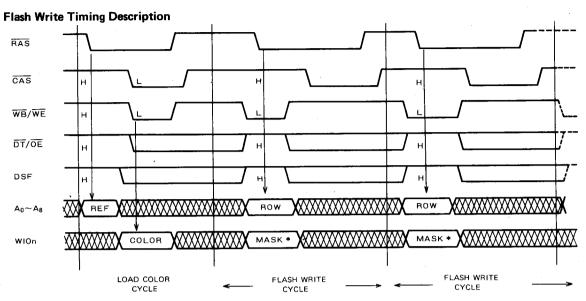

### 1. Flash Write

Utility: A high speed clear can be performed with flash write cycle.

\* Write a color (0 or 1) to an entire row in one RAM cycle.

Before flash write cycle, the color data must be set into an internal color register at least once.

This Material Copyrighted By Its Respective Manufacturer

4-80

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

The mask must be asserted on each flash write cycle.

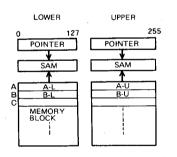

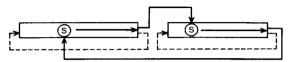

### 2. Split Register

### Utility

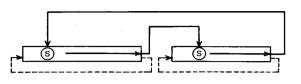

- a. To simplify real time transfer timing (Fully asynchronous Serial Access)

- Split Serial Register into two halves To optimize the memory size to CRT.

# DISPLAY

# **Pointer Path**

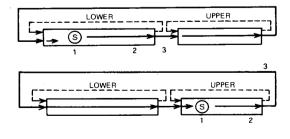

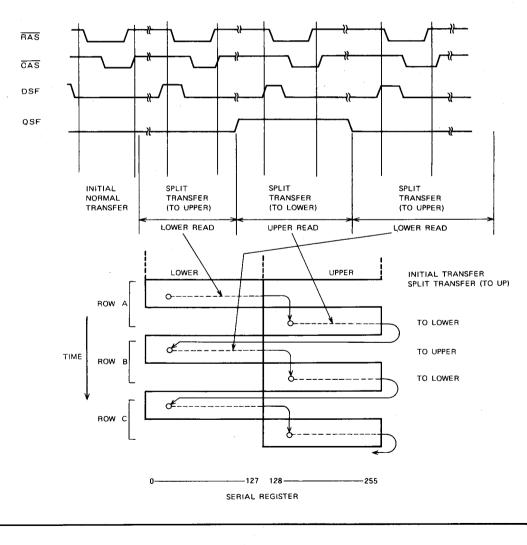

### At Normal read transfer cycle

- 1. Transfer the data from RAM to SAM, and set the SAM start address among 256.

- 2. Start the Serial Read cycle.

- Serial Read from Lower to Upper/Upper to Lower. (The pointer of the Lower/Upper SAM will be automatically cleared to address 0/128 after over-carried)

**MITSUBISHI LSIs**

M5M482128J-8, -10, -12

**1048576-BIT DUAL-PORT DYNAMIC RAM**

### At Split and read transfer cycle

- 1. Normal transfer cycle must be performed prior to the split transfer cycle.

- 2. The data is transfered between the idle half of the SAM and the selected Row. At the same time the idle SAM's start address is set to give the next start address after the end of the busy SAM.

- 3. At the split transfer mode, data is transfered to the idle half of the SAM automatically. (Column  $A_7$  is ignored.)

- 4. QSF indicates the busy SAM. (Lower Half SAM is busy: 0, Upper Half SAM is busy: 1)

- 5. Serial Read can be performed asynchronously during RAM cycle and Split transfer cycle.

### **1048576-BIT DUAL-PORT DYNAMIC RAM**

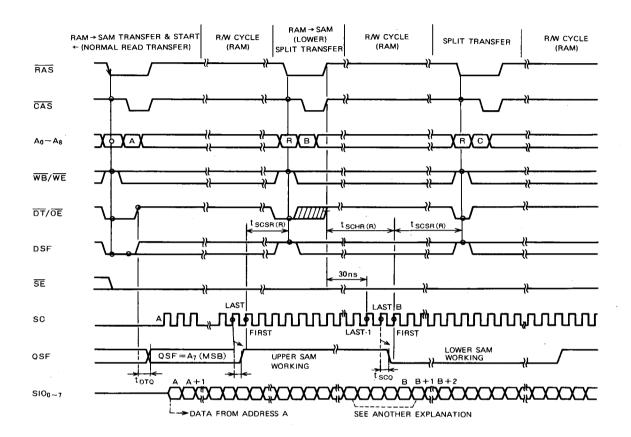

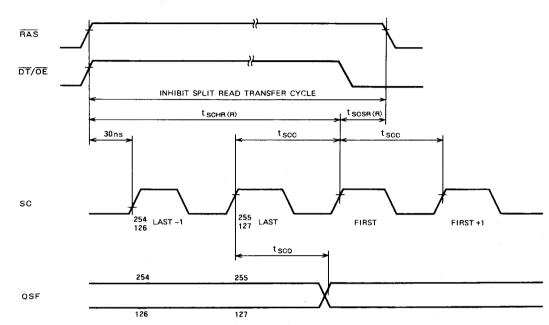

### Split Read Transfer Timing Description

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

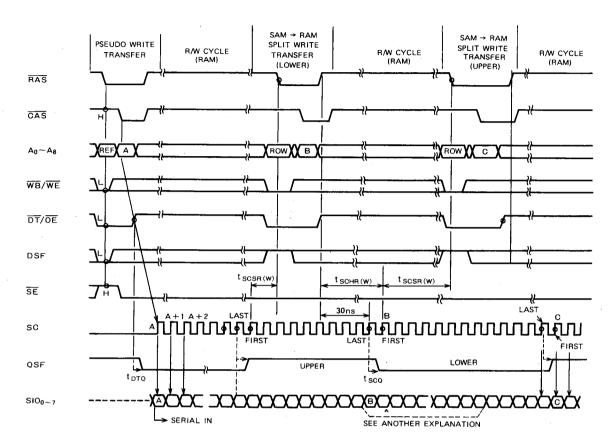

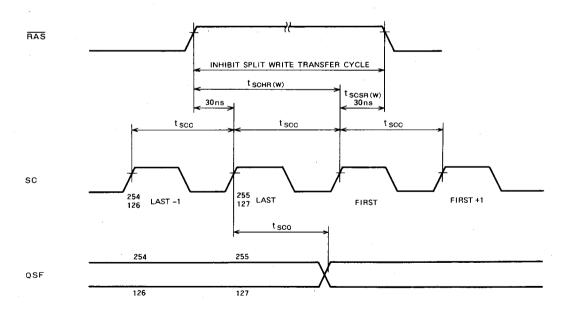

# Split Write Transfer Timing Description

4-84

Split Read Transfer Inhibit Timing Description

# Split Write Transfer Inhibit Timing Description

### **1048576-BIT DUAL-PORT DYNAMIC RAM**

# Serial-Out

| Data transfer mode    | SIO mode   | SAM TAP      | Data transfer | QSF set        |

|-----------------------|------------|--------------|---------------|----------------|

| Normal read transfer  | Output     | Col. (A0~A7) | RAM→SAM       | A7             |

| Normal write transfer | Input      | Col. (Ag~A7) | SAM→RAM       | Α <sub>7</sub> |

| Pseudo write transfer | Input      | Col. (A0~A7) | _             | Α7             |

| Split read transfer   | Not effect | Col. (A0~A6) | RAM-→SAM #1   |                |

| Split write transfer  | Not effect | Col. (Ag~A6) | SAM→RAM +1    | _              |

\*1: If QSF = 0 then the upper half data ( $128 \sim 255$ ) is transfered. If QSF = 1 then the lower half data ( $0 \sim 127$ ) is transfered.

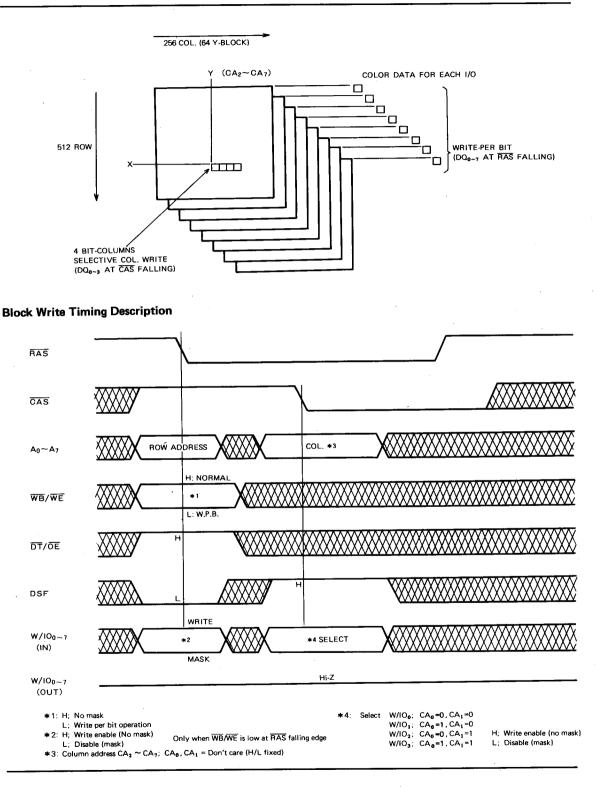

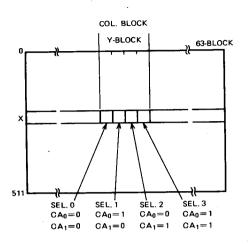

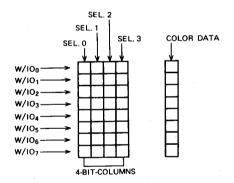

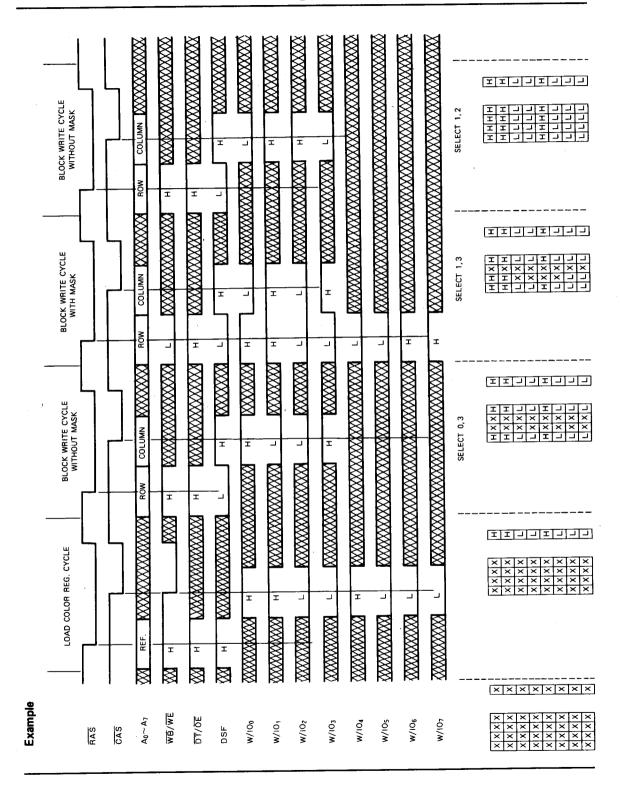

### 3. Block Write

4-86

In the Block Write cycle, Data from the Color Register can be written into 4 bit-columns (which Blocks are selected with column address  $CA_2 \sim CA_7$ ) at one time. The  $DQ_{0-3}$ the input at  $\overline{CAS}$  falling edge enables a selective column write operation of the selected 4 bit-columns.

When  $\overline{WB}/WE$  is low at  $\overline{RAS}$  falling edge Write-per-bit operation applies to the writing of color data.

The Color Register must be loaded prior to the Block Write cycle.

### Application

Block Write operation is useful for the partial-clearing or partial-painting of a bit-map display with same color data. With the selective-column writing of data, any of the 4 bit-columns can be masked, so allowing the boundary treatment in the same cycle.

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

This Material Copyrighted By Its Respective Manufacturer

4-87

### **1048576-BIT DUAL-PORT DYNAMIC RAM**

$A_0$ ,  $A_1$  and  $W/IO_{4-7}$  at  $\overline{CAS}$  falling edge, are "don't care", but must be set H or L state.

### Example of Block Write Operation

4-88

'X' indicates pre-state, 'H'; high level (1), 'L'; low level (0).

This Material Copyrighted By Its Respective Manufacturer

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

# ABSOLUTE MAXIMUM RATINGS

| Symbol         | Parameter             | Conditions                            | Ratings | Unit |

|----------------|-----------------------|---------------------------------------|---------|------|

| Vcc            | Supply voltage        |                                       | -1~7    | v    |

| V <sub>1</sub> | Input voltage         | With respect to V <sub>SS</sub>       | -1~7    | v    |

| Vo             | Output voltage        | · · · · · · · · · · · · · · · · · · · | -1~7    | v    |

| 1 <sub>0</sub> | Output current        |                                       | 50      | mA   |

| Pd             | Power dissipation     | Ta=25°C                               | 1000    | mW   |

| Topr           | Operating temperature |                                       | 0~70    | °C   |

| Tstg           | Storage temperature   |                                       | -65~150 | °C   |

### RECOMMENDED OPERATING CONDITIONS (Ta=0~70°C, unless otherwise noted) (Note 1)

| Symbol          | Parameter        |      | Limits |     |      |  |  |  |

|-----------------|------------------|------|--------|-----|------|--|--|--|

|                 | rarameter        | Min  | Norm   | Max | Unit |  |  |  |

| Vcc             | Supply voltage   | 4.5  | 5      | 5.5 | v    |  |  |  |

| V <sub>SS</sub> | Supply voltage   | 0    | 0      | 0   | v    |  |  |  |

| VIH             | High-level input | 2.4  |        | 6.5 | v    |  |  |  |

| VIL             | Low-level input  | -1.0 |        | 0.8 | v    |  |  |  |

Note 1: All voltage values are with respect to VSS.

# **ELECTRICAL CHARACTERISTICS**

| Symbol  | Parameter                                      | <b>T</b>                                 |      | Limits |     |      |  |  |

|---------|------------------------------------------------|------------------------------------------|------|--------|-----|------|--|--|

| Symbol  | Farameter                                      | Test conditions                          | Min  | Тур    | Max | Unit |  |  |

| Von (R) | High level output (RAM port)                   | $I_{OH(R)} = -1mA$                       | 2.4  |        | Vcc | v    |  |  |

| Vol (r) | Low level output (RAM port)                    | $I_{OL(R)} = 2.1 \text{mA}$              | 0    |        | 0.4 | v    |  |  |

| VOL (R) | High level output (Serial I <sub>O</sub> port) | $I_{OH(S)} = -1mA$                       | 2.4  |        | Vcc | v    |  |  |

| VOL(S)  | Low level output (Serial Io port)              | I <sub>OL(S)</sub> =2.1mA                | 0    |        | 0.4 | v    |  |  |

| loz     | Off-state output current                       | Q Floating 0 <vout<v<sub>CC</vout<v<sub> | -10  |        | 10  | μA   |  |  |

| 4       | Input current                                  | 0 <vin<v<sub>CC</vin<v<sub>              | - 10 |        | 10  | μA   |  |  |

**CAPACITANCE** ( $T_a = 25^{\circ}C$ , f = 1MHz,  $V_l = 25 mVmrs$ )

| Symbol | Pin name                                | Test conditions                                                   |     | Unit |     |      |

|--------|-----------------------------------------|-------------------------------------------------------------------|-----|------|-----|------|

| Symbol | ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) | Test conditions                                                   | Min | Тур  | Max | Unit |

| CINO   | RAS, CAS, WB/WE, SC, SE, DT/OE, DSF     |                                                                   | -   |      | 8   | pF   |

| CINI   | A <sub>0</sub> ~A <sub>8</sub>          | V <sub>I</sub> =V <sub>SS</sub> , f=1MHz, V <sub>I</sub> =25mVrms |     |      | . 8 | pF   |

| Co     | WIO0~WIO7, SIO0~SIO7, QSF               |                                                                   |     |      | 10  | pF   |

4---90

# ELECTRICAL CHARACTERISTICS (Ta=0~70°C, V<sub>CC</sub>=5V±10%, V<sub>SS</sub>=0V, unless otherwise noted) (Note 3)

|         |                                                                                                                            |                                |             | Limits       |                                                                                   |      |  |

|---------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|--------------|-----------------------------------------------------------------------------------|------|--|

| Symbol  | Parameter                                                                                                                  |                                | M5M482128-8 | M5M482128-10 | M5M482128-12                                                                      | Unit |  |

| oynibol | RAM port                                                                                                                   | SAM port                       | Max         | Мах          | M5M482128-12<br>Max<br>60<br>5<br>60<br>60<br>60<br>100<br>40<br>100<br>90<br>100 |      |  |

|         | Random R/W cycle RAS/CAS cycling, tRC = tRC (min)                                                                          | Standby (SC=VIL)               | 80          | 70           | 60                                                                                | mA   |  |

|         | Standby RAS = VIH, CAS = VIH, DOUT = HI-Z                                                                                  | (SC=V <sub>IL</sub> )          | 5           | 5            | 5                                                                                 | mA   |  |

| 1002    | $\overline{RAS}$ only refresh cycle $\overline{RAS}$ = cycling, $\overline{CAS}$ = V <sub>IH</sub> , t <sub>RC</sub> = min | $(SC = V_{IL})$                | 80          | 70           | 60                                                                                | mA   |  |

| 1003    | Page mode cycle $\overline{RAS} = V_{1L}$ , $\overline{CAS} = cycling$ , $t_{PC} = min$                                    | (SC=VIL)                       | 70          | 60           | 50                                                                                | mA   |  |

| 1005    | CAS before RAS refresh tBC = tBC (min)                                                                                     | (SC=VIL)                       | 80          | 70           | 60                                                                                | mΑ   |  |

| 1005    | Data transfer cycle tRC = tRC (min)                                                                                        | (SC=V <sub>IL</sub> )          | 80          | 70           | 60                                                                                | mA   |  |

| 1007    | Randam R/W cycle RAS/CAS cycling, tRc = tRc (min)                                                                          | Active (t <sub>SCC</sub> =min) | 140         | 120          | 100                                                                               | mA   |  |

| 1008    | Standby RAS = VIH, CAS = VIH, DOUT = Hi-Z                                                                                  | (t <sub>SCC</sub> = min)       | 60          | 50           | 40                                                                                | mA   |  |

| 1009    | RAS only refresh cycle RAS = cycling, CAS = V <sub>IH</sub> , t <sub>RC</sub> = min                                        | (t <sub>SCC</sub> = min)       | 140         | 120          | 100                                                                               | mA   |  |

| 1003    | Page mode cycle RAS = V <sub>IL</sub> , CAS = cycling, t <sub>RC</sub> = min                                               | (t <sub>SCC</sub> =min)        | 130         | 110          | 90                                                                                | mA   |  |

| LCC11   | CAS before RAS refresh tRC = tRC min                                                                                       | (t <sub>SCC</sub> =min)        | 140         | 120          | 100                                                                               | mA   |  |

|         | Data transfer cycle $t_{RC} = t_{RC}$ (min)                                                                                | (t <sub>SCC</sub> = min)       | 140         | 120          | 100                                                                               | mA   |  |

Note 3: ICC is obtained with the output open.

4: If V<sub>IH</sub> ≥ V<sub>CC</sub> × 0.9 and V<sub>IL</sub> ≤ 0.6V. Then 1<sub>CC2</sub> ≤ 2.0mA. (DSF, SE and SIO<sub>0</sub> ~ SIO<sub>7</sub> must be stable in high or low level.)

# SWITCH CHARACTERISTICS ( $T_a = 0 \sim 70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ , unless otherwise noted)

|                  |                                        |              |             |     | Lin   | nits    |       |      |    |

|------------------|----------------------------------------|--------------|-------------|-----|-------|---------|-------|------|----|

| Symbol           | Parameter                              |              | M5M482128-8 |     | M5M48 | 2128-10 | M5M48 | Unit |    |

| Symbol           |                                        |              | Min         | Max | Min   | Max     | Min   | Max  |    |

| tcac             | Access time from CAS                   | (Note 6, 7)  |             | 25  |       | 30      |       | 40   | ns |

| t <sub>RAC</sub> | Access time from RAS                   | (Note 6, 8)  |             | 80  |       | 100     |       | 120  | ns |

| t <sub>CAA</sub> | Column address access time             | (Note 6, 9)  |             | 40  |       | 50      |       | 60   | ns |

| t <sub>CPA</sub> | Access time from CAS precharge         | (Note 6, 10) |             | 45  |       | 55      |       | 65   | ns |

| toEA             | Access time from OE                    | (Note 6)     |             | 25  |       | 30      |       | 35   | ns |

| t <sub>CLZ</sub> | Output low impedance time from CAS low | (Note 6)     | 5           |     | 5     |         | 5     |      | ns |

| toFF             | Output disable time after CAS high     | (Note 11)    | 0           | 20  | 0     | 25      | 0     | 30   | ns |

| t <sub>OEZ</sub> | Output disable time after OE high      | (Note 11)    | 0           | 20  | 0     | 25      | 0     | 30   | ns |

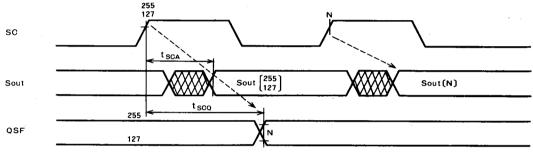

| t <sub>SCA</sub> | Access time from SC high               | (Note 6-S)   |             | 30  |       | 30      |       | 40   | ns |

| t <sub>SOA</sub> | Access time from SE low                | (Note 6-S)   | 0           | 25  | 0     | 25      | 0     | 35   | ns |

| tsoz             | Output disable time after SE high      | (Note 11)    | 0           | 20  | 0     | 20      | 0     | 25   | ns |

| t <sub>SOH</sub> | Serial outut hold time after SC high   |              | 5           |     | 5     |         | 5     |      | ns |

| t <sub>S00</sub> | Delay time SE low to serial setup      | (Note 6-S)   | 15          |     | 15    |         | 25    |      | ns |

Note 5: An initial pause of 500 µs is required after power-up followed by any 8 RAS or RAS/CAS cycles and 8 SC cycles before proper device operation is achieved. Note that RAS may be cycled during the initial pause.

And any 8 RAS or RAS/CAS cycles are required after prolonged periods of RAS inactivity before proper device operation is achieved. 6: Measured with a load circuit equivalent to 1TTL loads and 50pF.

6-S: Measured with a load circuit equivalent to 1TTL loads and 30pF.

7: Assume that  $t_{RCD}(max) \leq t_{RCD}$  and  $t_{RAD}(max) \geq t_{RAD}$ .

8: Assume that  $t_{RCD} \leq t_{RCD}(max)$  and  $t_{RAD} \leq t_{RAD}(max)$ .

9: Assume that  $t_{RCD} - t_{RAD} \leq t_{CAA}(max) - t_{CAC}(max)$  and  $t_{RCD} \geq t_{RCD}(max)$ .

Assume that t<sub>CP</sub> ≤ t<sub>CP(max</sub>) and t<sub>ASC</sub> ≥ t<sub>ASC(max</sub>).

Assume that t<sub>CP</sub> ≤ t<sub>CP(max</sub>) and t<sub>ASC</sub> ≥ t<sub>ASC(max</sub>).

t<sub>OFF(max</sub>), t<sub>SOZ(max</sub>) and t<sub>OEZ(max</sub>) define the time at which the output achieves the high impedance state (|I<sub>out</sub>| ≤ 10µA) and are not reference to V<sub>OH(min</sub>) or V<sub>OL(max</sub>).

# Read, Write, Refresh, Read/Write Transfer, Flash Write, Load Color and Fast Page Cycles

|                   |                                              |       |          | Lii   | mits     |       |          | ļ    |

|-------------------|----------------------------------------------|-------|----------|-------|----------|-------|----------|------|

| Symbol            | Parameter                                    | M5M   | 482128-8 | M5M48 | 82128-10 | M5M48 | 32128-12 | Unit |

|                   |                                              | Min   | Max      | Min   | Max      | Min   | Max      |      |

| t <sub>REF</sub>  | Refresh cycle time                           |       | 8        |       | 8        |       | 8        | ms   |

| t <sub>RP</sub>   | RAS high pulse width                         | 70    |          | 80    |          | 90    |          | ns   |

| t <sub>RCD</sub>  | Delay time RAS low to CAS low (Note 1        | I) 30 | 55       | 30    | 70       | 30    | 85       | ns   |

| t <sub>CRP</sub>  | Delay time CAS high to RAS low (Note 1       | 5) 10 |          | 10    |          | 10    |          | ns   |

| t <sub>CPN</sub>  | CAS high pulse width (Note 1                 | 5) 35 |          | 35    |          | 35    |          | ns   |

| t <sub>RAD</sub>  | Column address delay time from RAS (Note 1   | ') 20 | 40       | 20    | 50       | 20    | 60       | ns   |

| t <sub>ASR</sub>  | Row address setup time before RAS            | 0     |          | 0     | -        | 0     |          | ns   |

| tASC              | Column address setup time before CAS (Note 1 | 3) 5  | 10       | 5     | 15       | 5     | 20       | ns   |

| t <sub>RAH</sub>  | Row address hold time after RAS              | 15    |          | 15    |          | 15    |          | ns   |

| t <sub>CAH</sub>  | Column address hold time after CAS low       | 20    |          | 20    |          | 20    |          | กร   |

| t <sub>T</sub>    | Transition time (Note 1                      | )) 3  | 35       | 3     | 35       | 3     | 35       | ns   |

| twsR              | WB/WE setup time before RAS                  | 0     |          | 0     |          | 0     |          | ns   |

| t <sub>RWH</sub>  | WB/WE hold time after RAS                    | 15    |          | 15    |          | 15    |          | ns   |

| t <sub>dtrs</sub> | DT/OE setup time before RAS                  | 0     |          | 0     |          | 0     |          | ns   |

| t <sub>DTRH</sub> | DT/OE hold time after RAS                    | 15    |          | 15    |          | 15    |          | ns   |

| t <sub>FSR</sub>  | DSF setup time before RAS                    | 0     |          | 0     |          | 0     |          | ns   |

| t <sub>RFH</sub>  | DSF hold time after RAS                      | 15    |          | 15    |          | 15    |          | ns   |

| t <sub>FSC</sub>  | DSF setup time before CAS                    | 0     |          | 0     |          | 0     |          | ns   |

| t <sub>CFH</sub>  | DSF hold time after CAS                      | 20    | -        | 20    | [        | 20    |          | ns   |

| tws               | Write mask setup time before RAS             | 0     |          | 0     |          | 0     |          | ns   |

| t <sub>wн</sub>   | Write mask hold time after RAS               | 15    |          | 15    | 1        | 15    |          | ns   |

Note 12: The timing requirements are assumed t<sub>T</sub> = 5ns.

13: VIH (min) and VIL (max) are reference levels for measuring timing of input signals.

14: tRCD(max) is specified as a reference point only.

If tRCD is less than tRCD (max), access time is tRAC.

If  $t_{RCD}$  is greater than  $t_{RCD}$  into a line is defined as  $t_{CAC}$  and  $t_{CAA}$  as shown in notes 7, 9. 15:  $t_{CRP}$  requirement is applicable for all RAS/CAS cycles.

16: tCPN(min) is specified as tCPN(min) = tRCD(min) + tCRP(min) except for tCP of fast page mode cycle.

17: tRAD(max) is specified as a reference point only.

If  $t_{RAD} \ge t_{RAD}(max)$ , access time is assumed by  $t_{CAA}$  for read cycle.

18: tASC(max) is specified as a reference point only of address access time.

19: tT is measured between VIH (min) and VIL (max).

### **Read and Refresh Cycles**

|                   |                                                      |             |       | Lin   | nits    |       |         |      |

|-------------------|------------------------------------------------------|-------------|-------|-------|---------|-------|---------|------|

| Symbol            | Parameter                                            | M5M482128-8 |       | M5M48 | 2128-10 | M5M48 | 2128-12 | Unit |

|                   |                                                      | Max         | Min   | Min   | Max     | Min   | Max     |      |

| t <sub>BC</sub>   | Read cycle time                                      | 160         |       | 190   |         | 220   |         | ns   |

| tRAS              | RAS low pulse width                                  | 80          | 10000 | 100   | 10000   | 120   | 10000   | ns   |

| t <sub>CAS</sub>  | CAS low pulse width                                  | 25          | 10000 | 30    | 10000   | 35    | 10000   | ns   |

| t <sub>csH</sub>  | CAS hold time after RAS                              | 80          |       | 100   |         | 120   |         | ns   |

| t <sub>RSH</sub>  | RAS hold time after CAS                              | 25          |       | 30    |         | 35    |         | ns   |

| tRCS              | Read setup time before CAS                           | 0           |       | 0     |         | 0     |         | ns   |

| t <sub>RCH</sub>  | Read hold time after CAS high (Note 20)              | 0           |       | 0     |         | 0     |         | ns   |

| t <sub>RRH</sub>  | Read hold time after RAS high (Note 20)              | 10          |       | 10    |         | 10    |         | ns   |

| tRAL              | Column address to RAS setup time                     | 40          |       | 50    |         | 60    | ļ       | ns   |

| tRPC              | Precharge to CAS active time                         | 0           |       | 0     |         | 0     | ļ       | ns   |

| th (CLOE)         | OE hold time after CAS low                           | 25          |       | 30    |         | 35    |         | ns   |

| th (RLOE)         | OE hold time after RAS low                           | 80          |       | 100   |         | 120   | ļ       | ns   |

| TDOEL             | Delay time date to OE low                            | 0           |       | 0     |         | 0     |         | ns   |

| t <sub>OEHD</sub> | Delay time OE high to Data                           | 15          |       | 20    |         | 25    | ļ       | ns   |

| th (OECH)         | $\overline{CAS}$ hold time after $\overline{OE}$ low | 25          |       | 30    | L       | 35    |         | ns   |

| th (OERH)         | RAS hold time after OE low                           | 25          |       | 30    |         | 35    |         | กร   |

Note 20: Either tRCH or tRRH must be satisfied for a read cycle.

# Write Cycle (Eary Write and Delayed Write)

|                  |                                       |      |         | Lin          | nits  |              |       |      |  |

|------------------|---------------------------------------|------|---------|--------------|-------|--------------|-------|------|--|

| Symbol           | Parameter                             | M5M4 | 32128-8 | M5M482128-10 |       | M5M482128-12 |       | Unit |  |

| ·                |                                       | Min  | Max     | Min          | Max   | Min          | Max   |      |  |

| twc              | Write cycle time                      | 160  |         | 190          |       | 220          |       | ns   |  |

| t <sub>RAS</sub> | RAS low pulse width                   | 80   | 10000   | 100          | 10000 | 120          | 10000 | ns   |  |

| tCAS             | CAS low pulse width                   | 25   | 10000   | 30           | 10000 | 35           | 10000 | ns   |  |

| t <sub>CSH</sub> | CAS hold time after RAS               | 80   |         | 100          |       | 120          |       | ns   |  |

| tash             | RAS hold time after CAS               | 25   |         | 30           |       | 35           |       | ns   |  |

| twcs             | Write setup time before CAS (Note 22) | 0    |         | 0            |       | 0            |       | ns   |  |

| twch             | Write hold time after CAS             | 15   |         | 20           |       | 25           |       | ns   |  |

| tcwL             | CAS hold time after write             | 20   |         | 25           |       | 30           |       | ns   |  |

| TRWL             | RAS hold time after write             | 20   |         | 25           |       | 30           |       | ns   |  |

| twp              | Write pulse width                     | 15   |         | 20           |       | 25           |       | ns   |  |

| t <sub>DSC</sub> | Data setup time before CAS            | 0    |         | 0            |       | 0            |       | ns   |  |

| t <sub>DSW</sub> | Data setup time before write          | 0    |         | 0            |       | 0            |       | ns   |  |

| t DHC            | Data hold time after CAS              | 25   |         | 30           |       | 35           |       | ns   |  |

| t <sub>DHW</sub> | Data hold time after write            | 20   |         | 25           |       | 30           | L     | ns   |  |

| tOEHD            | Delay time OE high to data            | 25   |         | 30           |       | 35           |       | ns   |  |

| th(woe)          | OE hold time after write              | 20   |         | 25           |       | 30           |       | ns   |  |

|                   |                                                   |      | Limits    |              |       |              | 1     |      |

|-------------------|---------------------------------------------------|------|-----------|--------------|-------|--------------|-------|------|

| Symbol            | Parameter                                         | M5M4 | 82128-8   | M5M482128-10 |       | M5M482128-12 |       | Unit |

|                   |                                                   | Min  | Max       | Min          | Max   | Min          | Max   |      |

| tRWC              | Read write/read modify write cycle time (Note 21) | 205  |           | 245          |       | 285          |       | ns   |

| tRAS              | RAS low pulse width                               | 125  | 10000     | 155          | 10000 | 185          | 10000 | ns   |

| t <sub>CAS</sub>  | CAS low pulse width                               | 70.  | 10000     | 85           | 10000 | 100          | 10000 | ns   |

| t <sub>CSH</sub>  | CAS hold time after RAS                           | 125  |           | 155          |       | 185          |       | ns   |

| t <sub>RSH</sub>  | RAS hold time after CAS                           | 70   |           | 85           |       | 100          |       | ns   |

| t <sub>RCS</sub>  | Read setup time before CAS                        | 0    |           | 0            |       | 0            |       | ns   |

| t <sub>CWD</sub>  | Delay time. CAS to write (Note 22)                | 45   |           | 55           |       | 65           |       | ns   |

| t <sub>RWD</sub>  | Delay time. RAS to write (Note 22)                | 100  |           | 125          |       | 150          |       | ns   |

| tcw∟              | CAS hold time after write                         | 20   |           | 25           |       | 30           | · · · | ns   |

| TRWL              | RAS hold time after write                         | 20   |           | 25           |       | 30           |       | កទ   |

| twp               | Write pulse width                                 | 15   |           | 20           |       | 25           |       | ns   |

| t <sub>DSW</sub>  | Data setup time before write                      | 0    |           | 0            |       | 0            |       | ns   |

| t <sub>DHW</sub>  | Data hold time after write                        | 20   |           | 25           |       | 30           |       | ns   |

| tAWD              | Delay time address to write (Note 22)             | 60   |           | 75           |       | 90           |       | ns   |

| th (CLOE)         | OE hold time after CAS                            | 25   |           | 30           |       | 35           |       | ns   |

| th(RLOE)          | OE hold time after RAS                            | 80   |           | 100          |       | 120          |       | ns   |

| t DOEL            | Delay time. Data to OE low                        | 0    |           | 0            |       | 0            | • -   | ns   |

| t <sub>DEHD</sub> | Delay time. OE high to data                       | 15   | · · · · · | 20           |       | 25           |       | ns   |

| th (WOE)          | OE hold time after write low                      | 15   |           | 20           |       | 25           |       | ns   |

Note 21: tRWC is specified as tRWC(min) = tRAC(max) + tOEHD(min) + tRWL(min) + tRP(min) + 4tr.

22: twcs, tcwp, tRwp and tAwp are specified as reference points only.

$If twcs \ge twcs(min) \text{ the cycle is an early write cycle and the WIO pins will remain high impedance throughout the entire cycle. If tcwcb \ge tcWc(min), tewcb \ge tawcb (min) and tawcb \ge tawcb (min), the cycle is a read-modify-write cycle and the WIO will contain the data read from the selected address. If neither of the above conditions is satisfied, the condition of the WIO (at access time and until CAS or OE goes back to V<sub>H</sub>) is indeterminate.$

### Fast-Page Mode Cycle (Read, Early Write, Read-Write, Read-Modify-Write Cycle)

| Symbol<br>tpc<br>tras<br>tcas |                                          |      | / Limits |       |         |      |                                         |      |  |

|-------------------------------|------------------------------------------|------|----------|-------|---------|------|-----------------------------------------|------|--|

|                               | Parameter                                | M5M4 | 82128-8  | M5M48 | 2128-10 | M5M4 | 82128-12                                | Unit |  |

|                               |                                          | Min  | Max      | Min   | Max     | Min  | 82128-12<br>Max<br>100 k<br>10000<br>25 |      |  |

| t <sub>PC</sub>               | Read, write cycle time                   | 50   |          | 60    |         | 70   |                                         | ns   |  |

| t <sub>RWPC</sub>             | Read, write/read modify write cycle time | 100  |          | 115   |         | 135  |                                         | ns   |  |

| t RAS                         | RAS low pulse width for read write cycle | 135  | 100 k    | 160   | 100 k   | 190  | 100 k                                   | ns   |  |

| tCAS                          | CAS low pulse width for read cycle       | 25   | 10000    | 30    | 10000   | 35   | 10000                                   | ns   |  |

| t <sub>CP</sub>               | CAS high pulse width (Note 23)           | 10   | 15       | 10    | · 20    | 15   | 25                                      | ns   |  |

| t <sub>RSH</sub>              | RAS hold time after CAS                  | 25   | <u> </u> | · 30  |         | 35   |                                         | ns   |  |

Note 23:  $t_{CP(max)}$  is specified as a reference point only. If  $t_{CP(max)} \leq t_{CP}$ , access time is assumed by  $t_{CAC}$ .

# CAS before RAS Refresh Cycle (Note 24)

| Symbol           |                                           |      | Limits  |       |              |     |         |      |  |

|------------------|-------------------------------------------|------|---------|-------|--------------|-----|---------|------|--|

|                  | Parameter                                 | M5M4 | 82128-8 | M5M48 | M5M482128-10 |     | 2128-12 | Unit |  |

|                  |                                           | Min  | Max     | Min   | Max          | Min | Max     | -    |  |

| t <sub>CSR</sub> | CAS setup time for CAS before RAS refresh | 10   |         | 10    |              | 10  |         | ns   |  |

| t <sub>CHR</sub> | CAS hold time for CAS before RAS refresh  | 30   |         | 35    |              | 40  | 1       | ns   |  |

| t <sub>RPC</sub> | Precharge to CAS active time              | 0    |         | 0     |              | 0   | ! -     | ns   |  |

Note 24: Eight of more CAS before RAS cycl is nesessary for proper operation of CAS before RAS refresh mode.

4--94

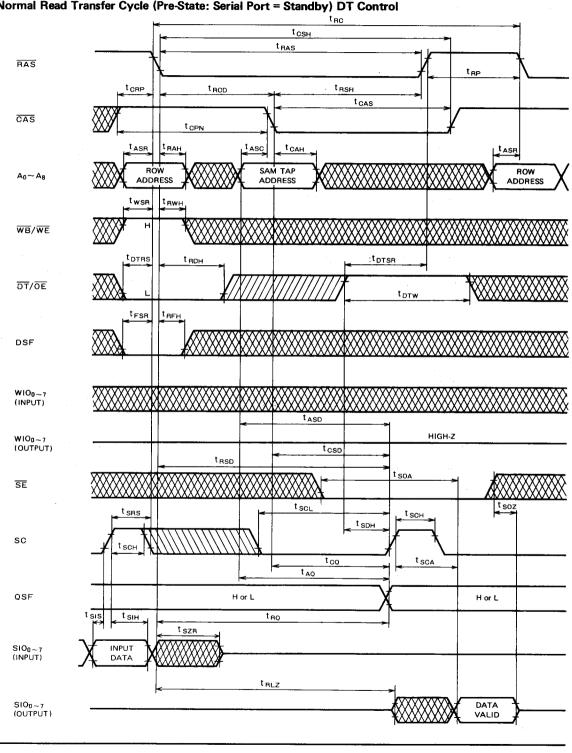

# Normal Read/Write/Pseudo Write Transfer

|                    |                                                                | Limits  |        |              |     |              |     |      |

|--------------------|----------------------------------------------------------------|---------|--------|--------------|-----|--------------|-----|------|

| Symbol             | Parameter                                                      | M 5M 48 | 2128-8 | M5M482128-10 |     | M5M482128-12 |     | Unit |

| 0,                 |                                                                | Min     | Max    | Min          | Max | Min          | Max |      |

| t <sub>RDH</sub> * | DT/OE low hold time after RAS                                  | 70      |        | 80           |     | 90           |     | ns   |

| t <sub>RSD</sub>   | Delay time RAS to SC                                           | 90      |        | 105          |     | 120          |     | ns   |

| tASD               | Delay time address to SC                                       | 55      |        | 60           |     | 65           |     | ns   |

| tcsp               | Delay time CAS to SC                                           | 50      |        | 55           |     | 60           |     | ns   |

| t SDH              | SC hold time after DT                                          | 15      |        | 15           |     | 20           |     | ns   |

| tRO                | Delay time RAS to QSF                                          |         | 105    |              | 125 |              | 140 | ns   |

| tAO                | Delay time address to QSF                                      |         | 70     |              | 80  |              | 85  | ns   |

| t <sub>co</sub>    | Delay time CAS to QSF                                          |         | 75     |              | 85  |              | 90  | ns   |

| t <sub>DTQ</sub>   | Delay time DT to QSF                                           |         | 30     |              | 35  |              | 40  | ns   |

| tDTSR              | DT high setup time before RAS high (Note 25)                   | 0       |        | 0            |     | 0            |     | ns   |

| tDTW               | DT high pulse width                                            | 20      |        | 25           |     | 30           |     | ns   |

| tes                | SE setup time before RAS low                                   | 0       |        | 0            |     | 0            |     | ns   |

| t <sub>EH</sub>    | SE hold time after RAS low                                     | 15      |        | 15           |     | 15           | L   | ns   |

| t <sub>SZR</sub>   | RAS low to serial input delay time (Serial-in → Serial-out)    | 20      |        | 20           |     | 20           |     | ns   |

| t <sub>RLZ</sub>   | RAS to serial output delay time (Serial-in → Serial-out)       | 25      |        | 25           |     | 25           |     | ns   |

| tsRS               | SC setup time before RAS low                                   | 30      |        | 35           |     | 40           |     | ns   |

| t <sub>SDZ</sub>   | Serial output turn-off delay from RAS (Serial-out → Serial-in) | 10      | 50     | 10           | 50  | 10           | 60  | ns   |

| t <sub>SDP</sub>   | RAS to serial input delay time (Serial-out → Serial-in)        | 50      |        | 50           |     | 60           |     | ns   |

★ If t<sub>RCD</sub> ≥ 70ns, t<sub>RDH</sub>(min) is 15ns.

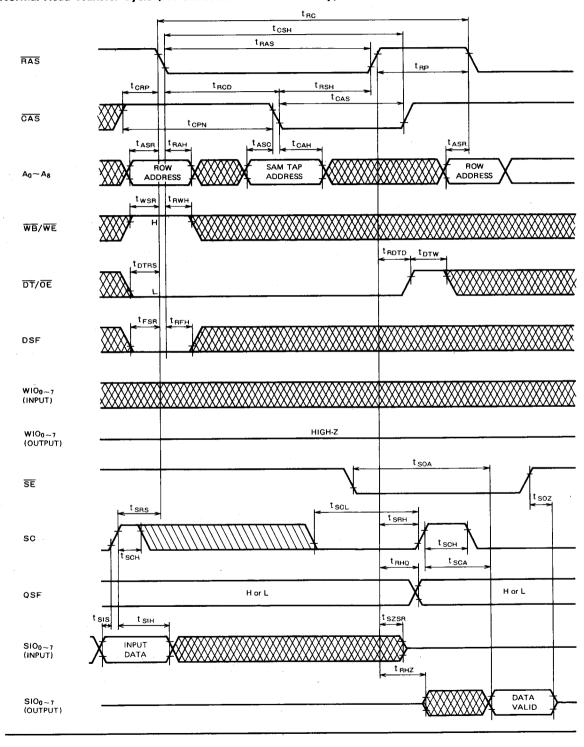

# **RAS** Control Read/Write/Pseudo Write Transfer

|                                                  | Parameter                                                                 |       | Limits      |     |       |         |       |                        |      |

|--------------------------------------------------|---------------------------------------------------------------------------|-------|-------------|-----|-------|---------|-------|------------------------|------|

| Symbol<br>tRDTD<br>tSRH<br>tDTW<br>tRHQ<br>tSZSR |                                                                           |       | M5M482128-8 |     | M5M48 | 2128-10 | M5M48 | 2128-12                | Unit |

|                                                  |                                                                           |       | Min         | Max | Min   | Max     | Min   | 182128-12<br>Max<br>40 |      |

| tвото                                            | DT hold time after RAS high (Not                                          | e 25) | 0           |     | 0     |         | 0     |                        | ns   |

|                                                  | SC hold time after RAS= high                                              |       | 20          |     | 20    |         | 25    |                        | ns   |

|                                                  | DT high pulse width                                                       |       | 20          |     | 25    |         | 30    |                        | ns   |

|                                                  | Delay time RAS high to QSF                                                |       |             | 30  |       | 30      |       | 40                     | กร   |

|                                                  | Delay time data to RAS high                                               |       | 0           |     | 0     |         | 0     |                        | ns   |

| t <sub>RHZ</sub>                                 | RAS high to serial output delay time (Serial-in $\rightarrow$ Serial-out) |       | 5           |     | 5     |         | 5     |                        | ns   |

Note 25:  $t_{RDTD(min)}$  and  $t_{DTSR(min)}$  are specified as a reference point only. If  $t_{RDTD} \ge t_{RDTD(min)}$ , the cycle is RAS control transfer cycle.

.

# Split Read/Write Transfer Cycle

| Symbol                |                                                     |              | Limits      |              |              |              |         |      |

|-----------------------|-----------------------------------------------------|--------------|-------------|--------------|--------------|--------------|---------|------|

|                       | Parameter                                           | M5M4         | M5M482128-8 |              | M5M482128-10 |              | 2128-12 | Unit |

|                       |                                                     | Min          | Max         | Min          | Max          | Min          | Max     |      |

| t SCSR (W)            | SC setup time to RAS at split write transfer cycle  | 30           |             | 30           |              | 40           |         | ns   |

| t SOHR (W)            | SC hold time from RAS at split write transfer cycle | tscc<br>+30  |             | tscc<br>+ 30 |              | tscc<br>+40  |         | ns   |

| t <sub>SCSR (R)</sub> | SC setup time to RAS at split read transfer cycle   | 0            |             | 0            |              | 0            |         | ns   |

| t <sub>SCHR (R)</sub> | SC hold time from RAS at split read transfer cycle  | 2tsoc<br>+30 |             | 2tscc<br>+30 | •            | 2tsoc<br>+40 |         | ns   |

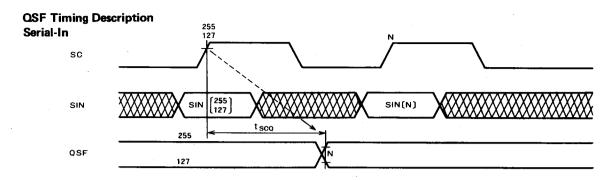

### Serial Input/Serial Output

|                     |                                             |       | Limits  |              |     |              |                     |        |

|---------------------|---------------------------------------------|-------|---------|--------------|-----|--------------|---------------------|--------|

| Symbol              | Parameter                                   | M5M4  | 82128-8 | M5M482128-10 |     | M5M482128-12 |                     | Unit   |

|                     |                                             | * Min | Мах     | Min          | Max | Min          | Max                 |        |

| t <sub>SSC(R)</sub> | SC clock cycte time (Serial Read)           | 30    |         | 30           | 1   | 40           |                     | ns     |

| t scc(w)            | SC clock cycte time (Serial Write)          | 30    |         | 40           |     | 40           |                     | ns     |

| t <sub>SCH</sub>    | SC high pulse width                         | 10    |         | 10           | -   | 15           |                     | ns     |

| t <sub>SCL</sub>    | SC low pulse width                          | . 10  |         | 10           |     | 15           | 1 1                 | ns     |

| t <sub>sop</sub>    | SE high pulse width                         | 25    |         | 25           |     | 35           |                     | ns     |

| t <sub>SOE</sub>    | SE low pulse width                          | 25    |         | 25           | 1   | 35           | <u> </u> − <u> </u> | ns     |

| t <sub>SIM</sub>    | Serial input data hold time after SC high   | 20    |         | 20           |     | 30           |                     | ns     |

| tsis                | Serial input data setup time before SC high | 0     |         | 0            |     | 0            |                     | <br>ns |

| t <sub>swin</sub>   | SE disable hold time after SC high          | 15    |         | 15           |     | 20           |                     | ns     |

| t <sub>swis</sub>   | SE disable setup time before SC high        | 10    | ~       | 10           |     | 10           |                     | ns     |

| t <sub>swn</sub>    | SE enable hold time after SC high •         | 15    |         | 15           |     | 20           |                     | ns     |

| t <sub>sws</sub>    | SE enable setup time before SC high         | 10    | -       | 10           |     | 10           |                     | ns     |

| tscq                | Delay time SC to QSF                        |       | 30      |              | 30  |              | 40                  | ns     |

# **Read Time Read Transfer**

4-96

|                   | •                                      | Limits |         |       |              |      |              |            |  |

|-------------------|----------------------------------------|--------|---------|-------|--------------|------|--------------|------------|--|

| Symbol            | Parameter                              |        | 82128-8 | M5M48 | M5M482128-10 |      | M5M482128-12 |            |  |

|                   |                                        | Min    | Max     | Min   | Max          | Min  | Max          |            |  |

| t <sub>RDH</sub>  | DT hold time after RAS                 | 70     |         | 85    |              | 100  |              | ns         |  |

| t <sub>CDH</sub>  | DT hold time after CAS                 | 30     |         | 35    | 1            | . 40 |              | ns         |  |

| t ADH             | DT hold time after address             | 35     |         | 40    |              | 45   |              | ns         |  |

| t <sub>SDD</sub>  | Delay time SC to DT                    | 20     | 1       | 20    |              | 25   |              | ns         |  |

| t <sub>SDH</sub>  | SC hold time after DT                  | 30     |         | 30    | 1            | 35   | † †          | ns         |  |

| t <sub>DTQ</sub>  | Delay time DT to QSF (Note 25)         |        | 30      |       | 30           |      | 40           | пз         |  |

| t <sub>RDTD</sub> | DT hold time after RAS high            | 0      |         | 0     |              | 0    |              | ns         |  |

| t <sub>SRD</sub>  | Delay time SC to RAS high (Note 25)    | 15     |         | 15    | 1            | 20   | 1            | ns         |  |

| t <sub>SRH</sub>  | SC hold time after RAS high (Note 25)  | 35     |         | 35    |              | 40   |              | ns         |  |

| t <sub>RHQ</sub>  | Delay time RAS high to QSF . (Note 25) |        | 30      |       | 30           |      | 40           | n <b>s</b> |  |

This Material Copyrighted By Its Respective Manufacturer

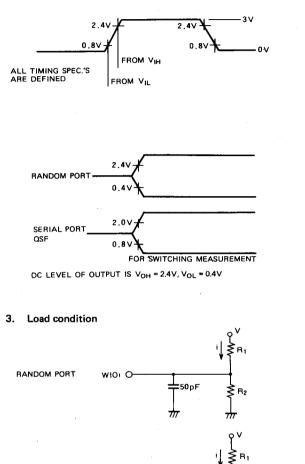

### Switching Measurement Condition

1. Input reference point

SERIAL PORT

⊥\_\_\_\_\_30<sub>p</sub>F

₹R2

SIOI O

$$R_1 = \frac{V_{OH}(V - V_{OL}) - V_{OL}(V - V_{OH})}{V_{OH} \cdot I_{OL} - V_{OL} \cdot I_{OH}}$$

$$R_2 = \frac{V_{OH} \cdot R_1}{(V - V_{OH}) - I_{OH} \cdot R_1}$$

**1048576-BIT DUAL-PORT DYNAMIC RAM**

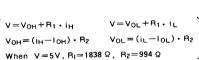

TIMING DIAGRAMS

4-98

**MITSUBISHI LSIs**

M5M482128J-8, -10, -12

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

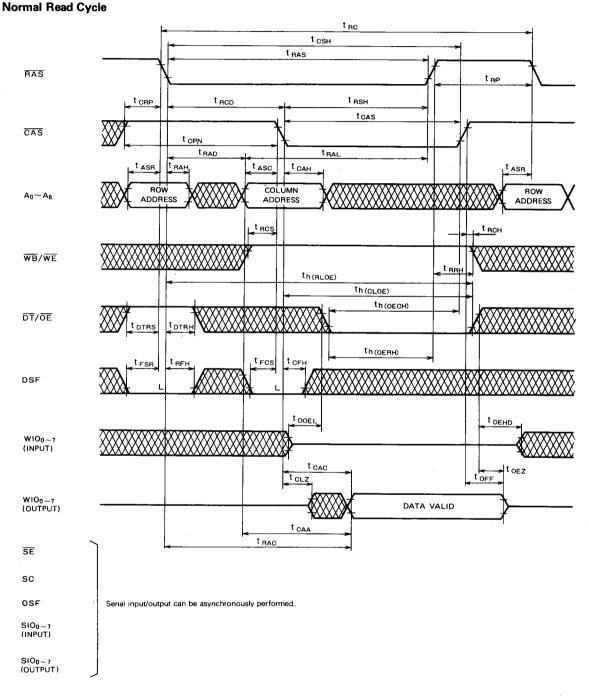

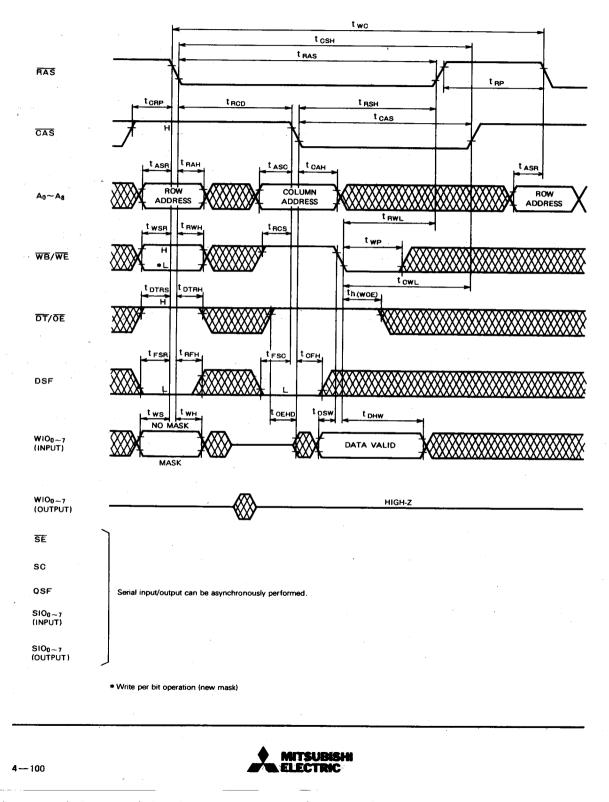

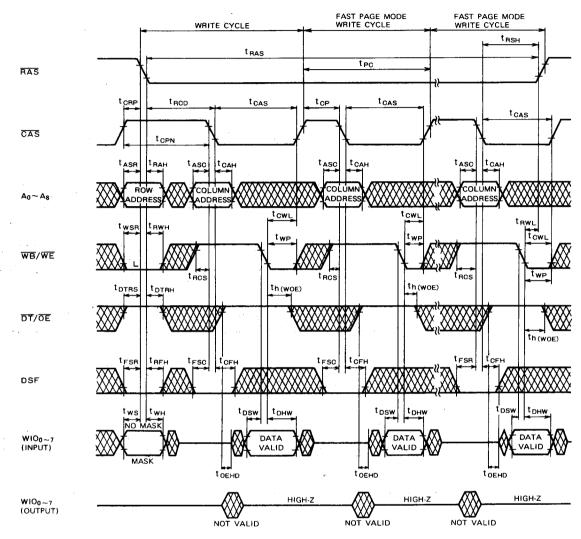

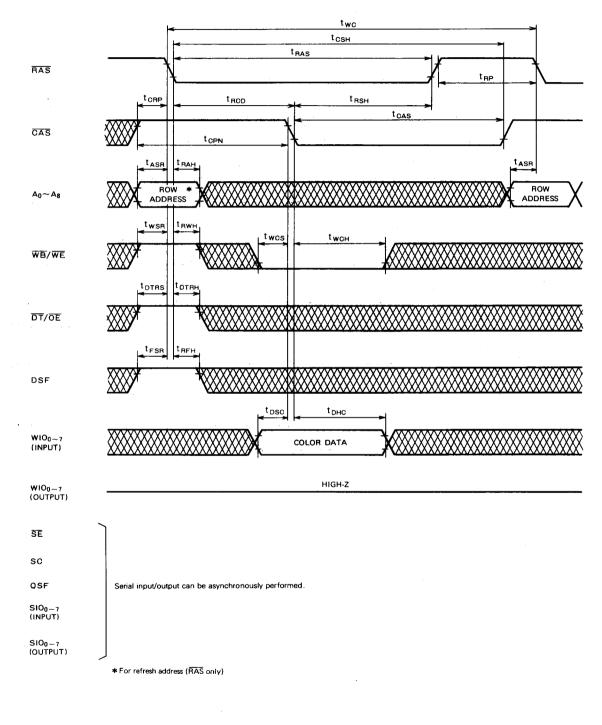

### Normal Write Cycle (Early Write)

# 1048576-BIT DUAL-PORT DYNAMIC RAM

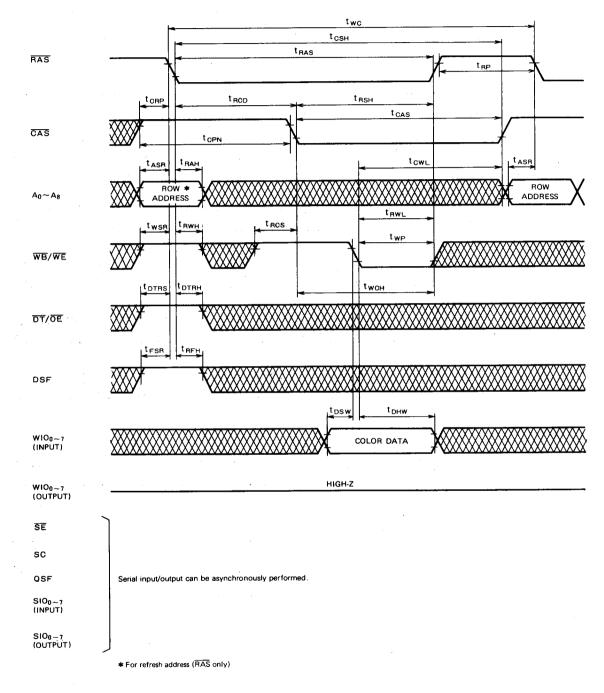

# Normal Write Cycle (Late Write)

This Material Copyrighted By Its Respective Manufacturer

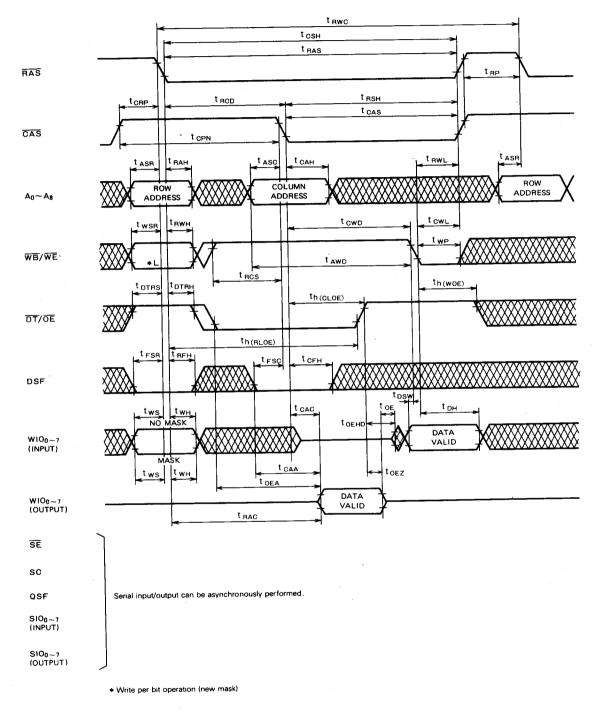

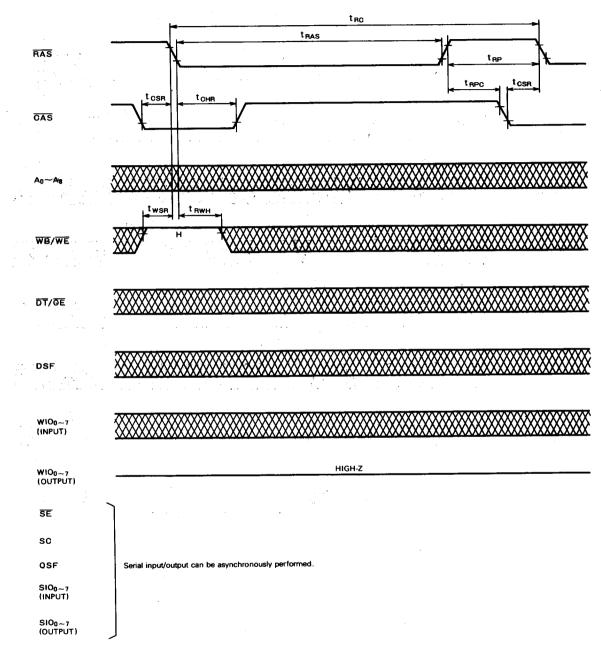

# Normal Read Modify Write Cycle

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

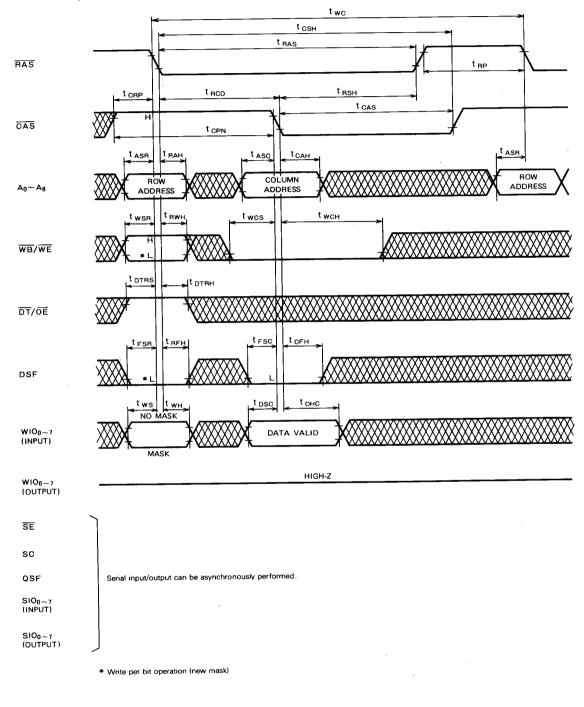

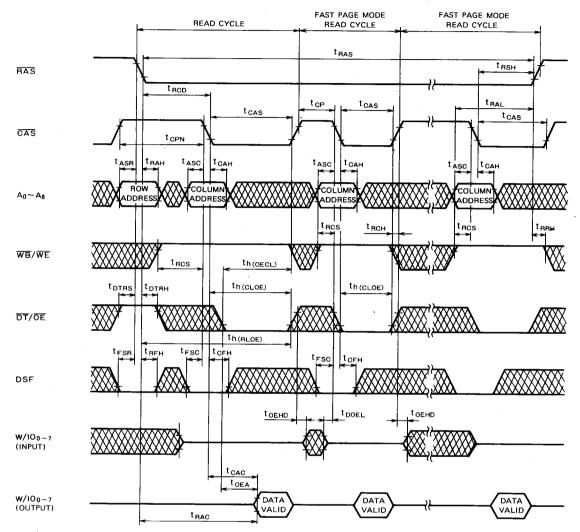

### Fast Page Mode Read Cycle

This Material Copyrighted By Its Respective Manufacturer

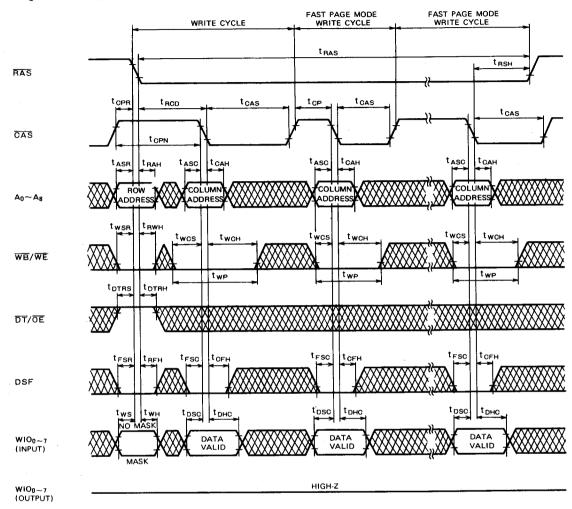

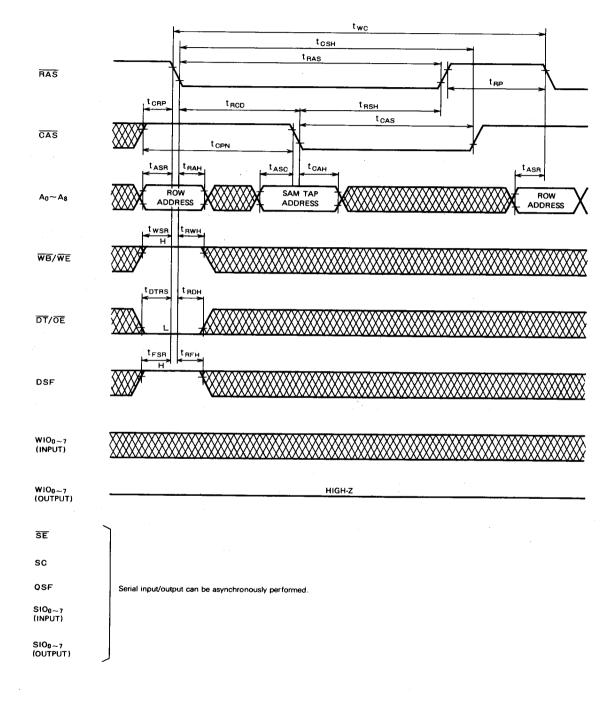

### Fast Page Mode Early Write Cycle with New Mask

Serial input/output can be asynchronously performed. Write per bit operation mask is effective during the continuous page mode cycle.

## **1048576-BIT DUAL-PORT DYNAMIC RAM**

# Fast Page Mode Late Write with New Mask

Serial input/output can be asynchronously performed. Write per bit operation mask is effective during the continuous page mode cycle.

M5M482128J-8, -10, -12

### TELEBRACE AND A STATE 1048576-BIT DUAL-PORT DYNAMIC RAM

### FAST PAGE READ-MODIFY-WRITE-CYCLE FAST PAGE WRITE-CYCLE READ-MODIFY-WRITE-CYCLE tRSH ters . . . . RAS t<sub>RWPC</sub> t CRP t RCD t CAS tcas tCAS CAS t <sub>CPN</sub> tcp t ASC tcy t<sub>RAH</sub> t <sub>CAH</sub> 198 COLUMN COLUM co ROW ADDRES An~As ADDRES ADDRES tow tow t<sub>RCS</sub> th(CLOE) th (OLOE) tRGS twr WB/WE tCAA th (CLOE) RCS t CAA t<sub>CAA</sub> t. ٩C t RAC t CAC toE/ t OEA ۰. DT/OE th (WOE) th (WOE) th (WOE) t DTRS DTRH toend t OEHD OFHD tFSC t<sub>FSC</sub> t, I CEH DSF tosw t DHM tosv t<sub>DHW</sub> tosw tD ws NO MASK DATA DATA DATA W100-7 VALIE VALID (INPUT) VALID MASK toez toez toez HIGH-Z HIGH-Z WIO0~7 (OUTPUT) VALID DATA VALID DATA VALID DATA

Fast Page Mode Read-Write, Read-Modify-Write-Cycle

1 1

1. 我们们最高兴的好的。

Serial input/output can be asynchronously performed. Write per bit operation mask is effective during the continuous page mode cycle.

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

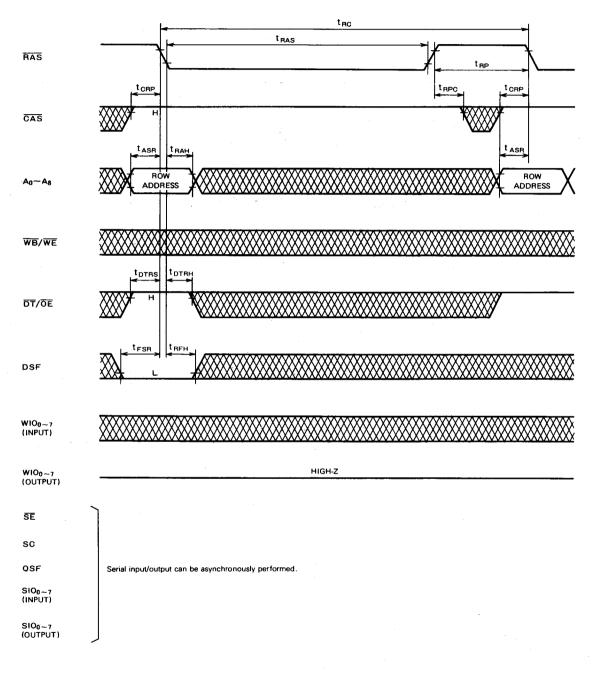

# **RAS** only Refresh Cycle

# 1048576-BIT DUAL-PORT DYNAMIC RAM

# CAS before RAS Refresh Cycle

1.1. 1.5 2. 1.

1.1

This Material Copyrighted By Its Respective Manufacturer

4-107

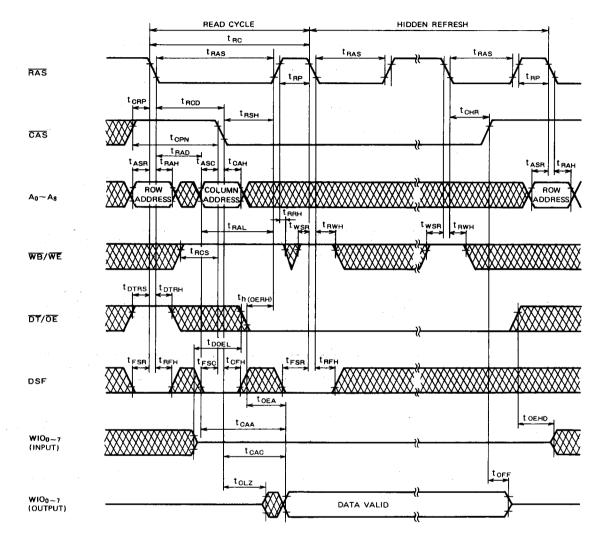

### Hidden Refresh Cycle (Automatic Refresh)

Serial input/output can be asynchronously performed.

# 1048576-BIT DUAL-PORT DYNAMIC RAM

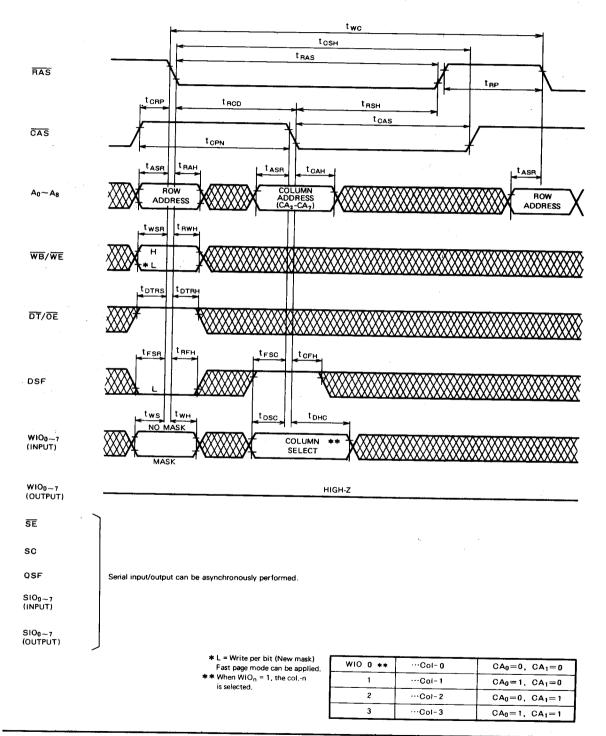

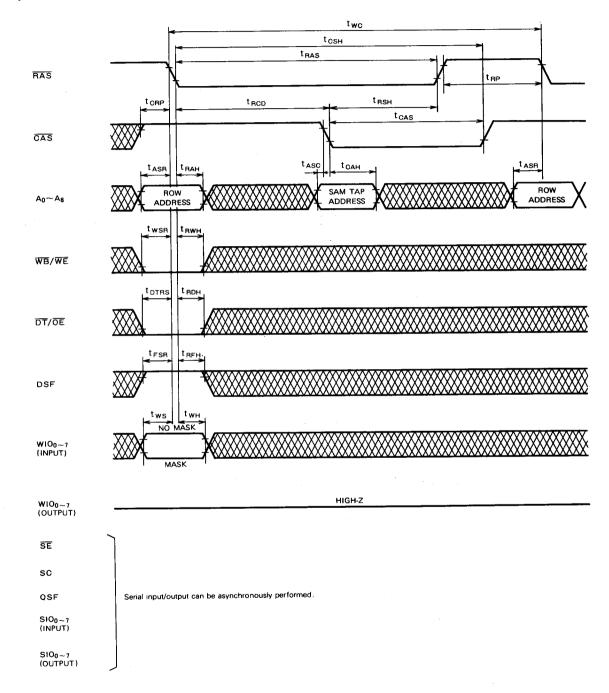

# **Block Write Cycle**

# **1048576-BIT DUAL-PORT DYNAMIC RAM**

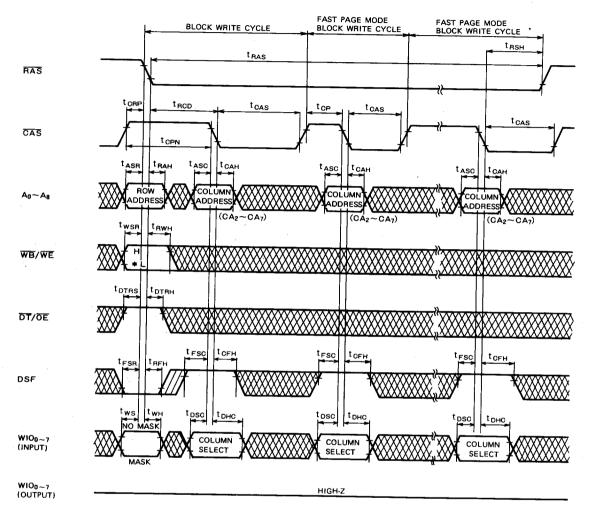

# Fast Page Mode Block Write Cycle

Serial input/output can be asynchronously performed.

This Material Copyrighted By Its Respective Manufacturer

4---110

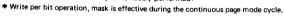

### Flash Write with Mask

# Load Color Register Cycle (Early Write, CAS Latch Data)

### Load Color Register Cycle (Late Write, Write Latch)

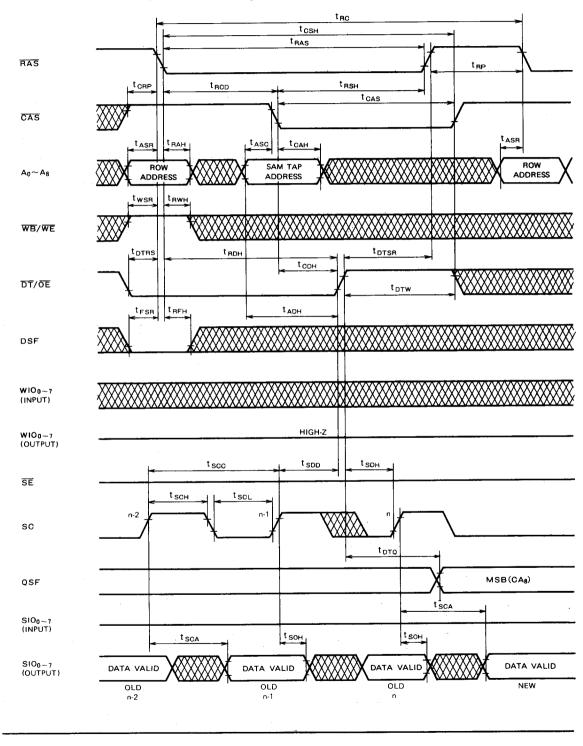

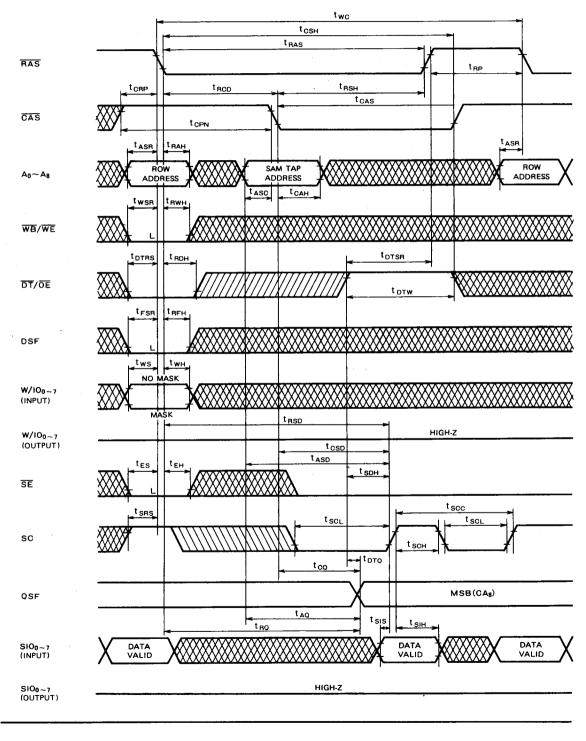

Normal Read Transfer Cycle (Pre-State: Serial Port = Standby) DT Control

## Normal Read Transfer Cycle (Pre-State: Serial Port = Standby) RAS Control

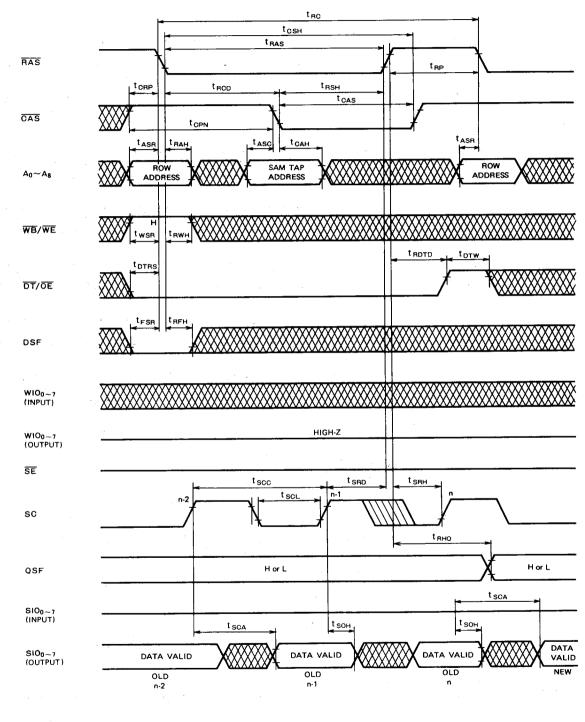

# Read-Time Read Transfer Cycle (To Active Register: Serial Port Active) DT Control

# Real-Time Read Transfer Cycle (To Active Register: Serial Port Active) RAS Control

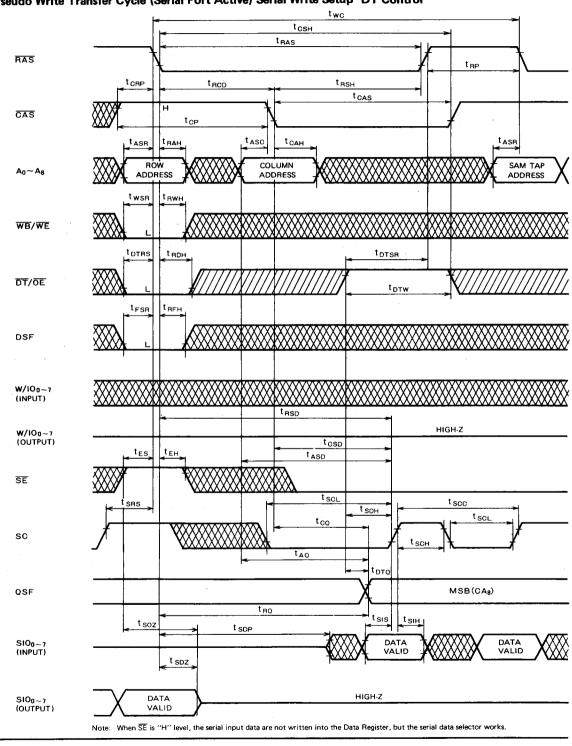

#### Pseudo Write Transfer Cycle (Serial Port Active) Serial Write Setup DT Control

# Pseudo Write Transfer Cycle (Serial Port Active) Serial Write Setup RAS Control

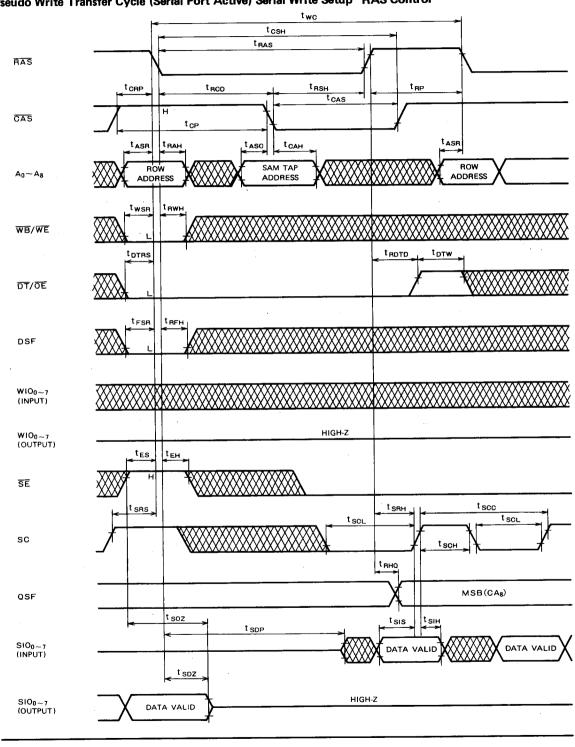

### Write Transfer Cycle (Serial Port = Write Cycle) with New Mask DT Control

# Write Transfer Cycle (Serial Port = Write Cycle) with New Mask RAS Control

## MITSUBISHI LSIS M5M482128J-8, -10, -12

### **1048576-BIT DUAL-PORT DYNAMIC RAM**

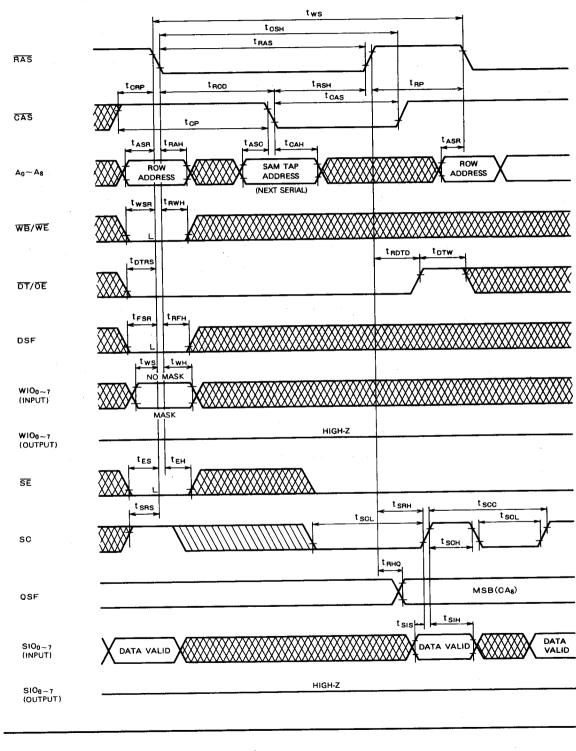

## Split Read Transfer (to Inactive Register)

This Material Copyrighted By Its Respective Manufacturer

## Split Write Transfer Cycle (to Inactive Register) with New Mask

Serial Write Cycle (SC Toggling,  $\overline{SE} = L$ )

This Material Copyrighted By Its Respective Manufacturer